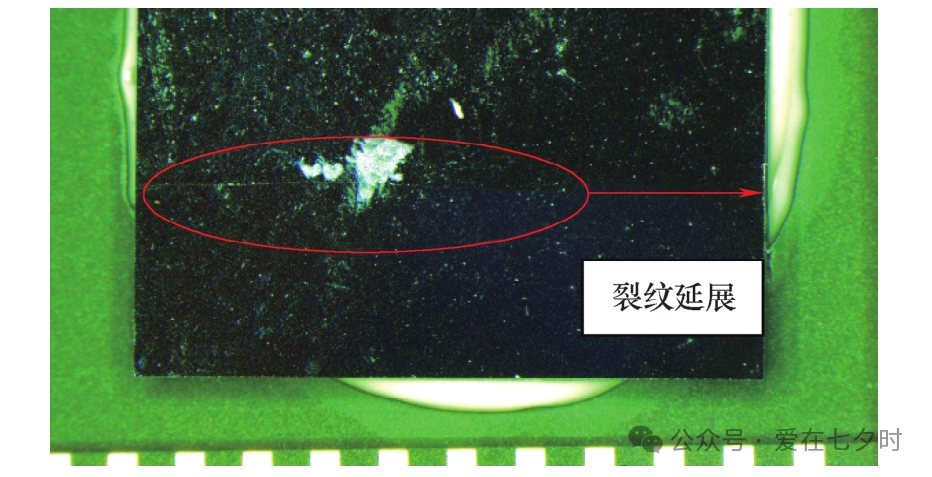

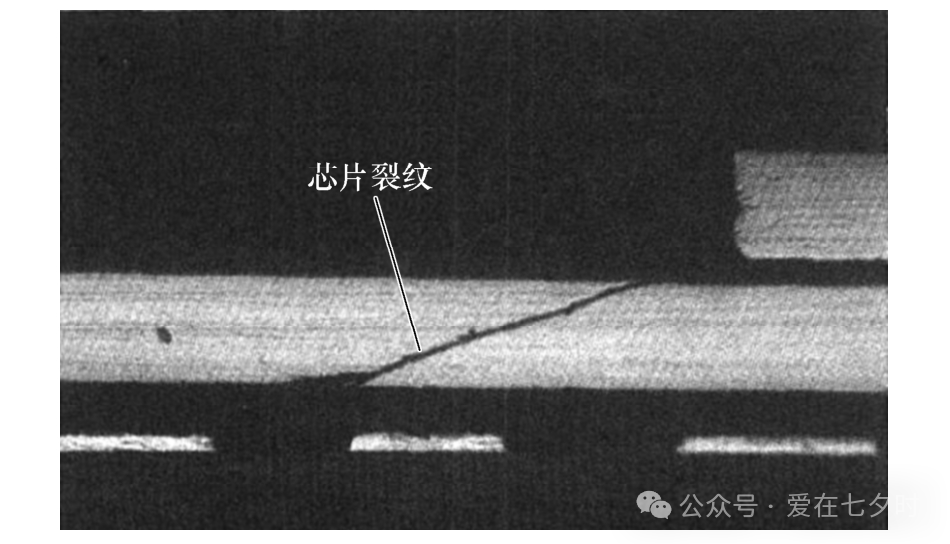

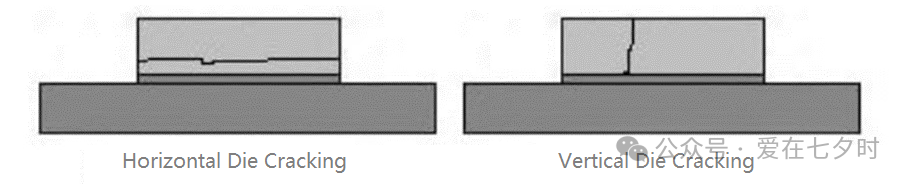

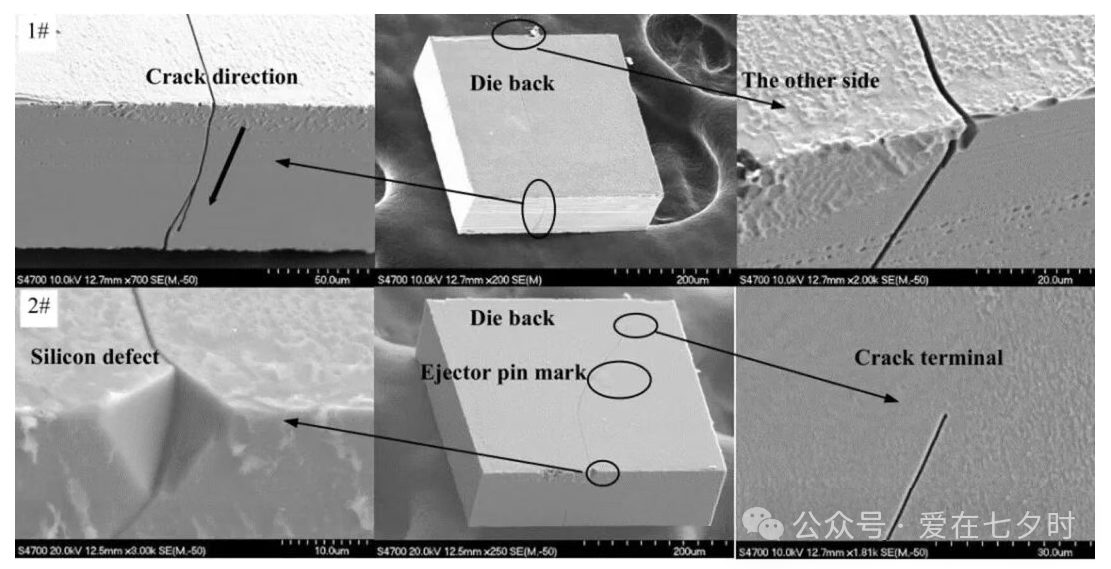

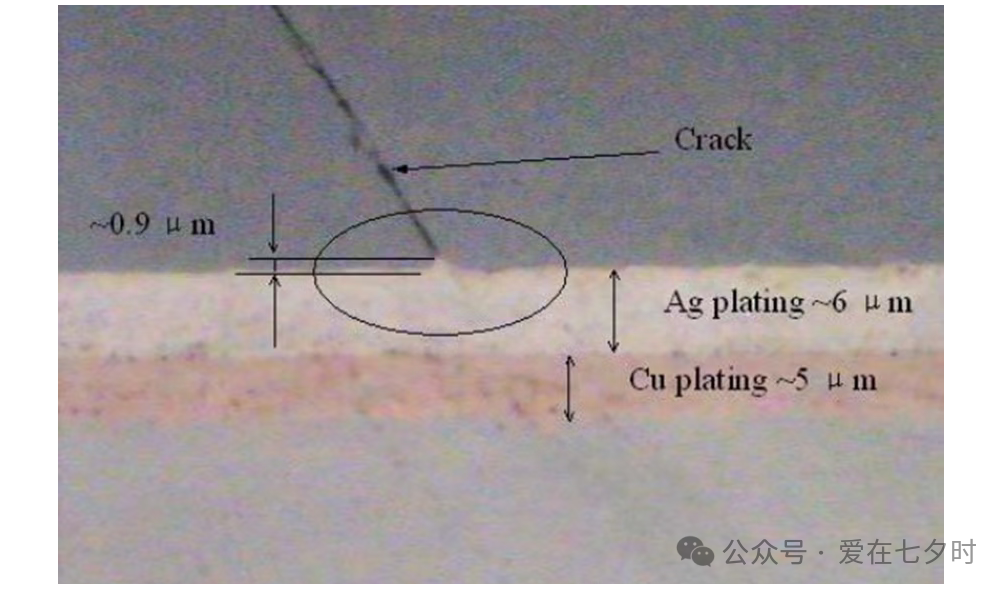

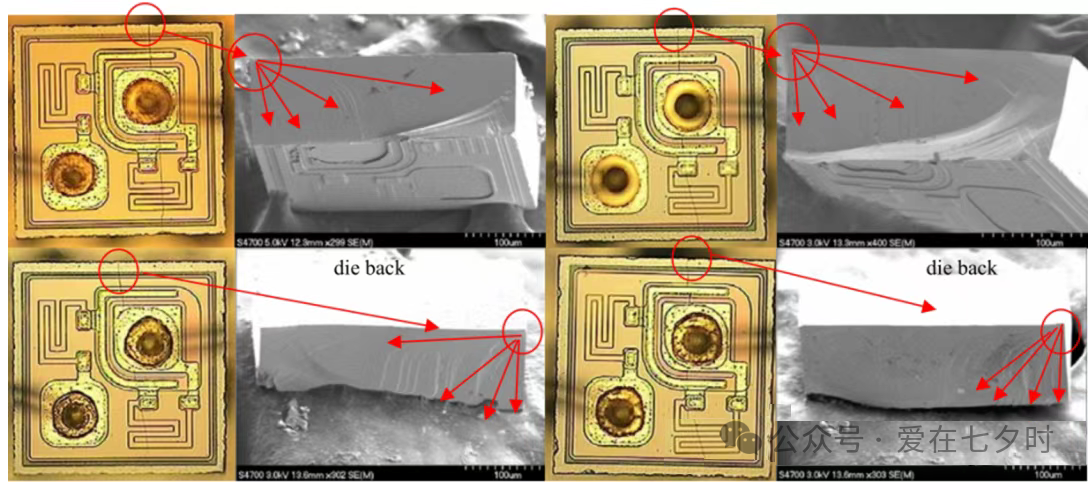

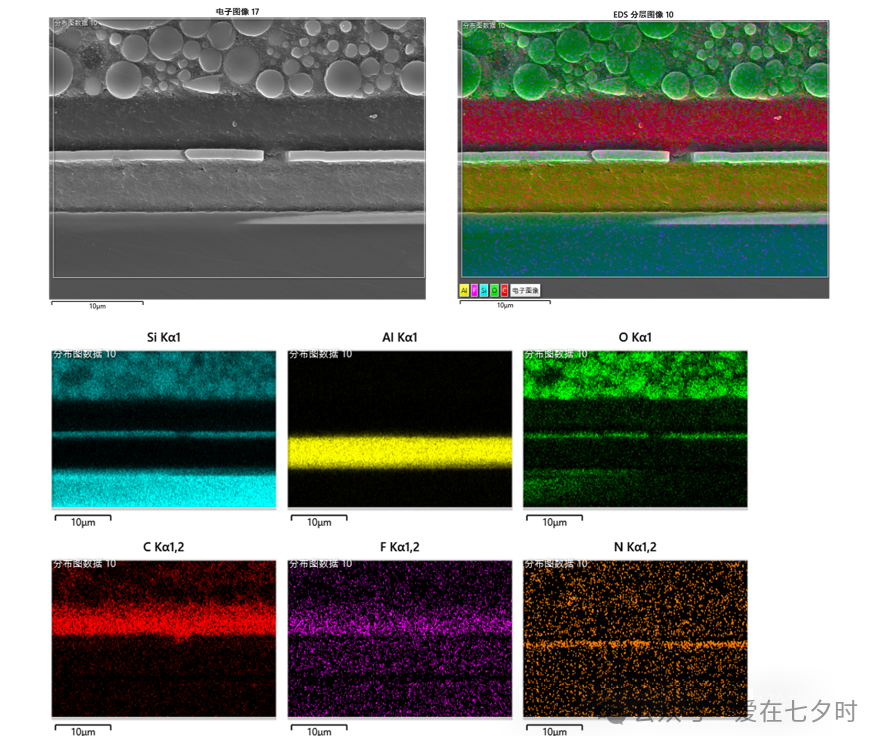

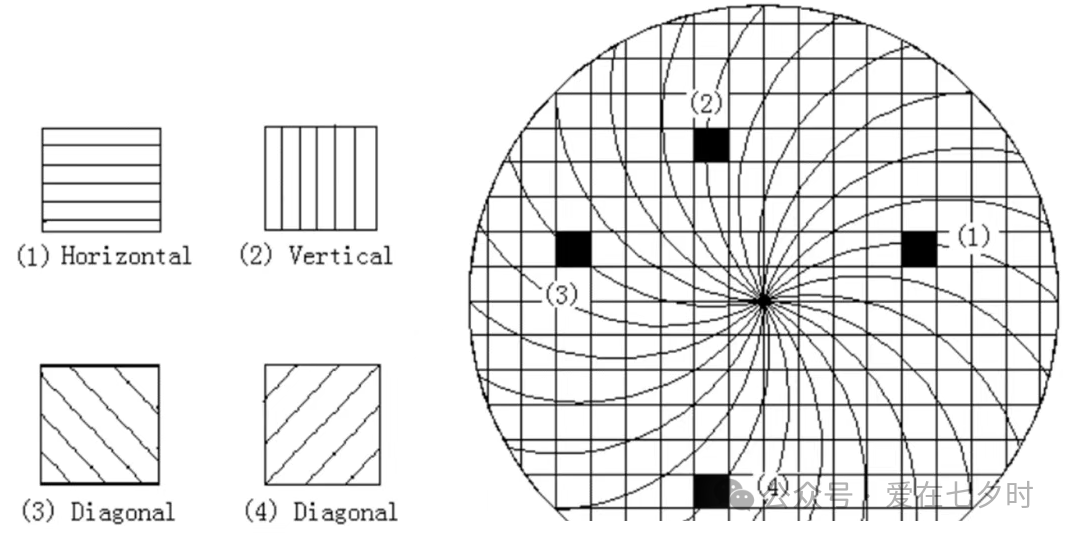

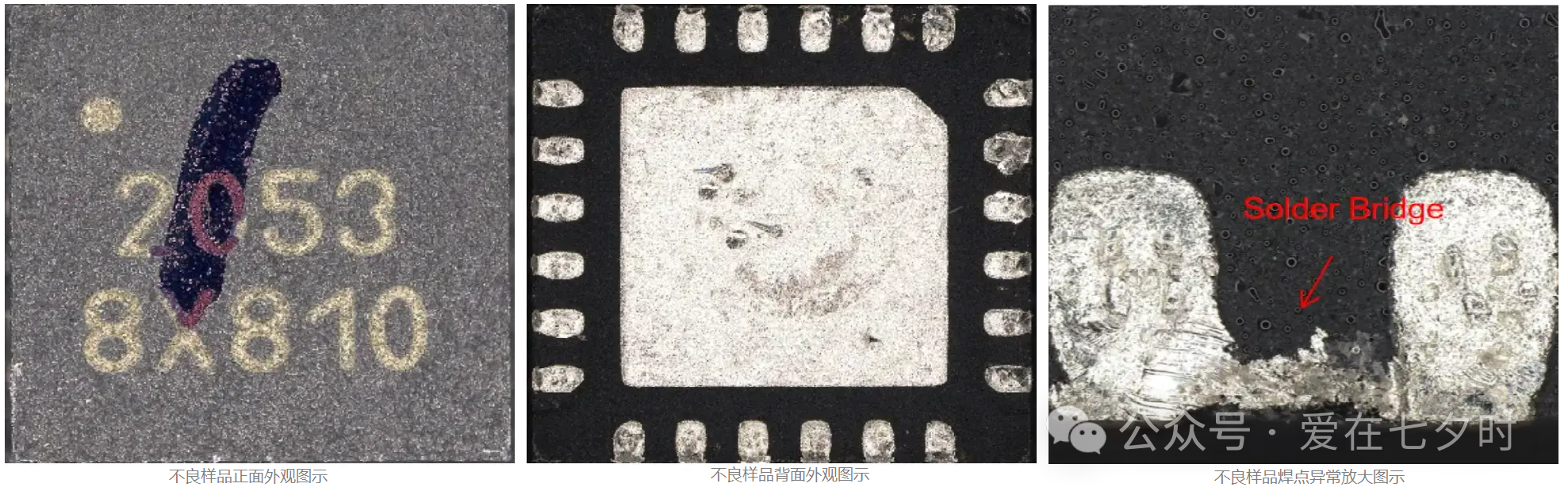

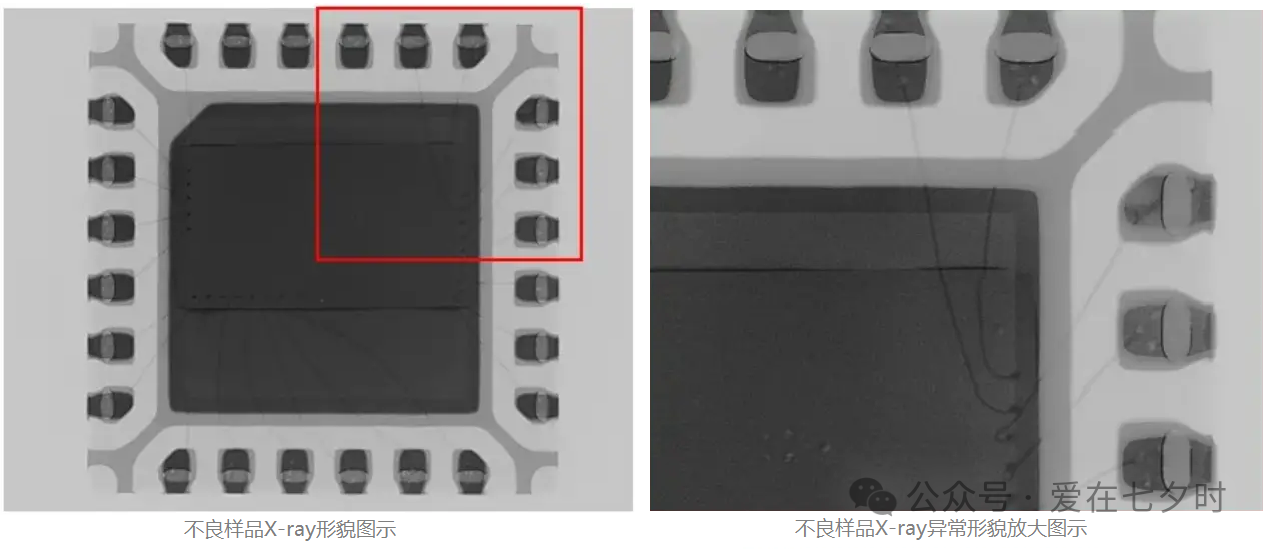

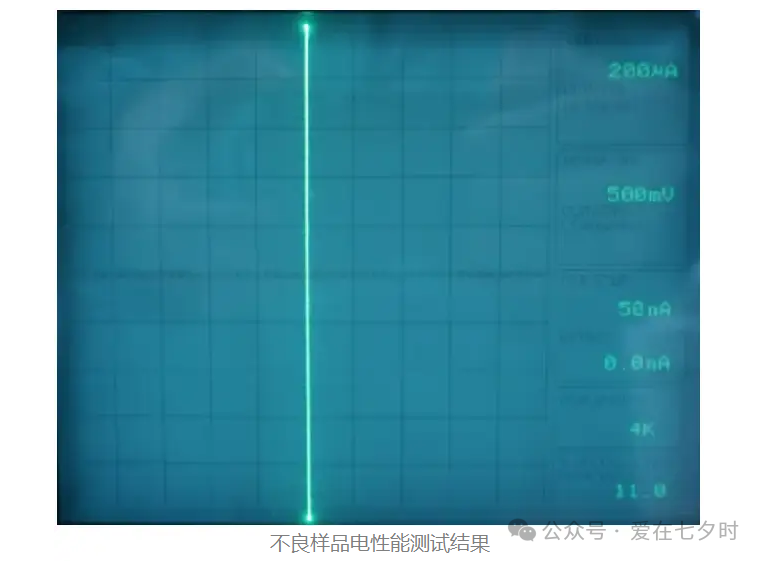

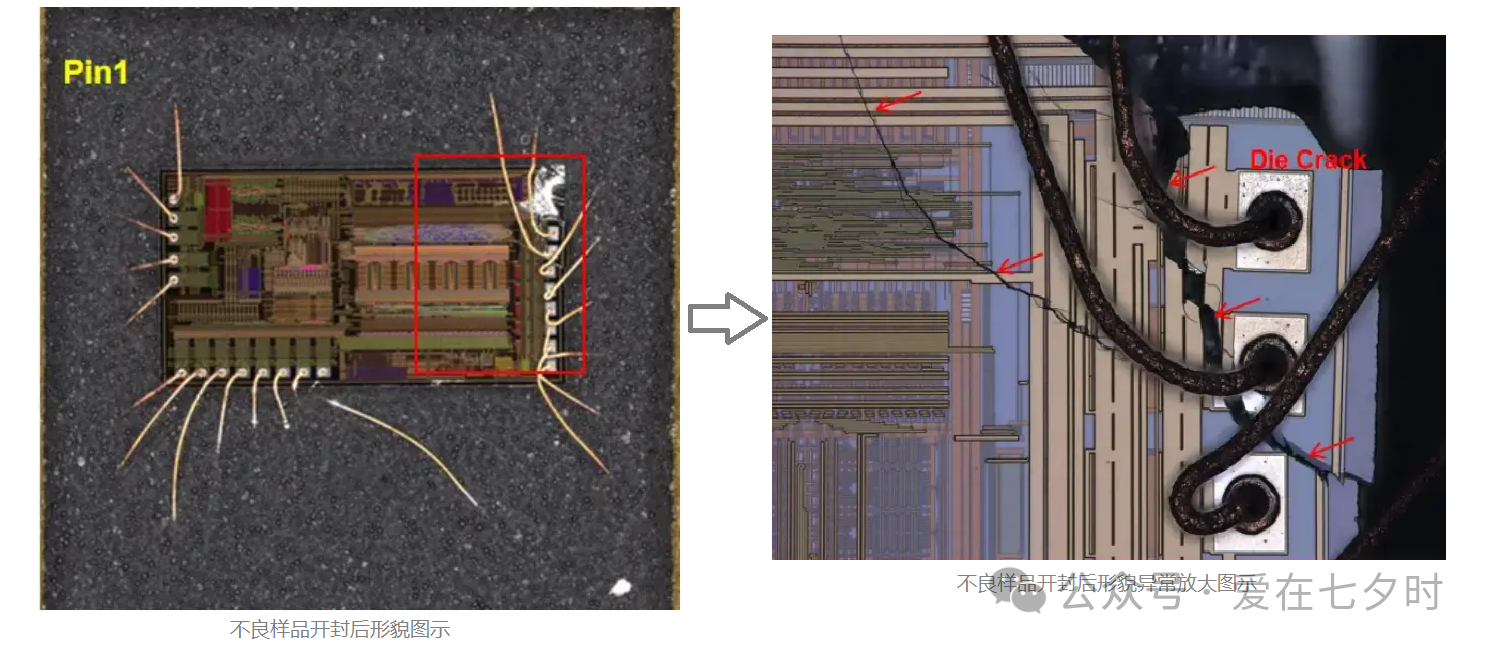

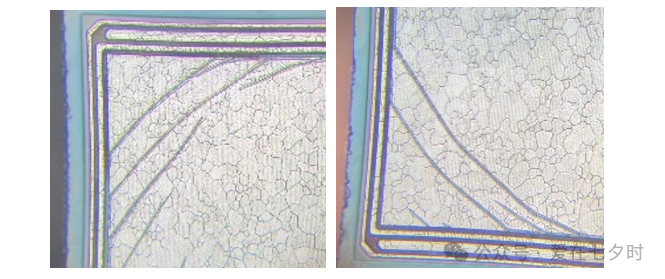

【博主简介】本人系一名半导体行业质量管理从业者,旨在业余时间不定期的分享半导体行业中的:产品质量、失效分析、可靠性分析和产品基础应用等相关知识。常言:真知不问出处,所分享的内容如有雷同或是不当之处,还请大家海涵,如有需要可留意文末联系方式,当前在网络平台上均以“爱在七夕时”的昵称为ID跟大家一起交流学习!相信在半导体封装工序工作的朋友,肯定对“芯片裂纹”(也有的叫芯片开裂或是裸片裂纹)这种非常典型的失效模式并不陌生。随着集成电路(IC)技术的发展,芯片尺寸不断缩小,厚度持续降低。这在提升单位晶圆产出、降低封装高度的同时,也带来了新的挑战。硅片的易碎特性使其在组装和测试过程中,即便受到中等强度的应力,也可能发生开裂。 而且更让人疑惑的是:DB、WB和Molding乃至后面的Final Test都没啥问题,Test Yield也可能会达标。但是,一经过可靠性的高低温循环测试,突然就可能有比较大量的芯片失效,拆开塑封料一看,硅片上全是从边缘延伸的裂纹。这种 “电测看不破,循环现原形” 的缺陷,堪称封装环节的 “隐形杀手”,也是一种导致灾难性的产品失效,每年能给行业造成的损失超十几亿,甚至更多。 所以,本章节想要跟大家分享的就是芯片封装中典型失效之一的“芯片裂纹”模式。会从硅芯片的 “先天脆弱性” 入手,拆解裂纹产生的工艺诱因、检测难点,再给出行之有效的工艺改进方案等等。  一、芯片裂纹的定义 芯片裂纹,英文常常称作:Die Crack,中文定义也可称作:裸片裂纹或是芯片开裂。它是指在半导体集成电路封装过程中或使用过程中,芯片表面或内部产生的开裂(裂纹)的一种现象。  二、芯片裂纹(Die Crack)的分类 当前按开裂(裂纹)方向去定义的话,主要分为以下两大类: 1、垂直方向裂纹 起源于芯片背面,通常由芯片弯曲,导致其背面受到拉伸应力而产生。裂纹从背面缺陷处(如研磨划痕)开始,并向芯片表面扩展。这种模式需要较大的应力才能触发。 2、水平/边缘裂纹 多由晶圆切片过程中形成的边缘缺陷引发,裂纹从边缘向芯片内部扩展,常见于倒装芯片(PBA)封装中,也是较为常见的模式。  三、芯片裂纹(Die Crack)产生的原因 芯片裂纹(Die Crack)的根源,首先在于硅本身的 “材质特性”—— 咱们常说单晶硅是 “硬而脆” 的典型,这可不是随口说的,而是由它的晶体结构和力学性能决定的。 1、芯片裂纹(Die Crack)的失效机理 从晶体结构来看,单晶硅是金刚石型面心立方结构,原子间通过强共价键结合,这种结构让它硬度极高(莫氏硬度 7,仅次于蓝宝石),但也导致它 “缺乏塑性”—— 一旦受到外力或应力,原子没办法通过滑移来缓解,只能在应力集中处形成裂纹,而且裂纹会沿着原子结合力较弱的 “解理面”(比如 {111} 晶面)快速扩展,最后导致脆断。就像玻璃一样,哪怕只是表面有个微小划痕,稍微受力就会碎。  从力学性能来看,硅的关键指标 “断裂韧性(KIC)” 极低,仅 0.7-1.0 MPa・m^1/2,而金属铜的断裂韧性是它的 50 倍以上。这意味着,硅芯片只要表面存在微米级的微裂纹(比如减薄后留下的 1μm 划痕),在很小的应力(比如 100MPa)作用下,裂纹就会瞬间扩展。更麻烦的是,硅的热膨胀系数(CTE)仅 3.5×10^-6/℃,和封装里的环氧塑封料(12-18×10^-6/℃)、引线框架铜(17×10^-6/℃)差异巨大,温度变化时产生的热应力,会成为裂纹扩展的 “助推器”。 简单来说,因为IC 裸芯片的制造原料通常均为单晶硅,因为特殊特性,在遭受外力作用或表面存在瑕疵时,极容易出现破裂情况。在晶圆减薄、晶圆切割、芯片贴装和引线键合等一系列需要施加应力的工艺操作过程中,芯片开裂的风险大幅增加,这一问题已成为致使 IC 封装失效的重要因素之一。 若芯片裂纹(Die Crack)未蔓延至引线区域,通过常规手段很难发现;更有部分存在裂纹的芯片,在常规工艺检查与电学性能检测时,其性能表现与正常芯片并无明显差异,使得裂纹问题极易被忽略。然而,这些隐藏的裂纹会对封装后器件的稳定性与使用寿命造成严重威胁。由于常规电学性能测试无法有效识别芯片裂纹(Die Crack),因此需要借助高低温热循环实验进行检测。在加热和冷却交替过程中,材料间产生的热应力会促使裂纹逐步扩展,直至芯片彻底破裂,最终在电学性能上呈现出异常状态。 鉴于外部应力是引发芯片裂纹(Die Crack)的主因,一旦检测到芯片存在裂纹,就必须立即对芯片封装的工艺流程和参数进行优化,最大程度减少工艺环节对芯片产生的应力影响。例如,在晶圆减薄工序中,采用更为精细的加工方式,提高芯片表面的平整度,以此消除潜在应力;晶圆切割时,运用激光切割技术替代传统方法,降低切割过程对芯片表面造成的应力损伤;在引线键合环节,精准调控键合温度和压力参数,确保键合过程平稳安全。 因此,硅芯片表面不能有瑕疵,也经不起剧烈的温度变化 —— 这是它容易开裂的先天因素,也是我们后续工艺控制的核心依据。  2、芯片裂纹(Die Crack)的影响 芯片裂纹(Die Crack)的失效模式多种多样,所以,失效的影响也各有不同,主要包括: a.电性能失效 当裂纹穿过结区时,可能导致短路或者漏电,这是最常见的失效表现。例如在表面贴装MOSFET产品中,经过SMT工艺后发现的D、S间漏电和短路现象,超过50%的失效比例都是由芯片内部裂纹引起的。 b.电路中断失效 裂纹也可能全部或者部分截断电路,造成器件功能完全丧失。 c.潜在性失效 最为致命的是,裂纹引起的这些效应只有当有热或者电流通过时才会显现,而标准的电性能测试则根本无法检测到这些失效。 从统计数据来看,芯片碎裂在早期失效中约占1%的比例,而对于使用薄/超薄芯片的器件(如IC卡),芯片碎裂则占其失效总数的一半以上。裂纹形状多为"十"字、"T"字型,亦有一部分为横贯芯片的单条裂纹,约50%以上的碎裂芯片,其裂纹位于芯片中央附近并垂直于边缘;其余芯片的裂纹则靠近芯片边缘或集中于芯片一角。  四、芯片裂纹(Die Crack)的来源 芯片裂纹(Die Crack)不是单一环节导致的,而是从晶圆减薄到引线键合,每个需要施加应力的环节,都可能埋下 “裂纹种子”。所以,芯片裂纹(Die Crack)的产生是多种因素共同作用的结果,可以归纳为内在因素和外在因素两大类。内在因素主要指芯片自身的强度特性,而外在因素则包括制造工艺和环境应力等方面的影响。 1、工艺过程中的应力源 a.晶圆减薄(Wafer Thinning) 为了适配薄型封装(比如手机芯片的 0.8mm 封装),晶圆需要从原始的 775μm 减薄到 50-100μm,这个过程中最容易产生微裂纹。传统的 “机械研磨”(用金刚石砂轮打磨),会在硅片表面留下深度 1-5μm 的 “机械损伤层”—— 这里面全是微小的划痕和晶格畸变,就像给芯片表面划了无数道 “隐形伤口”。 有测试数据显示,用 800 目砂轮机械减薄的晶圆,表面微裂纹密度能达到 100 个 /cm²,而后续工艺只要施加轻微应力(比如切割时的 20MPa 压力),这些微裂纹就会扩展成肉眼可见的大裂纹。更隐蔽的是,有些微裂纹在硅片内部(亚表面裂纹),减薄后根本看不出来,要到后续热循环时才会爆发。 b.晶圆切割(Wafer Dicing) 晶圆切割是把整片晶圆切成单个芯片,这个环节的应力最直接。目前主流的切割方式有两种,都有开裂风险。 c.机械刀片切割(mechanical blade cutting) 高速旋转的金刚石刀片(转速 30000rpm)在切割时,会对芯片边缘产生 “挤压应力” 和 “摩擦热应力”。如果刀片磨损(刃口变钝),或者切割压力过大(超过 50N),很容易在芯片边缘形成 “崩边”(边缘缺角),进而引发裂纹; d.激光切割(Laser cutting) 虽然没有机械接触,但高功率激光(比如 UV 激光)会在硅片表面产生局部高温(瞬间达 1000℃以上),冷却后形成 “热应力梯度”—— 表面收缩、内部膨胀,导致微裂纹产生。尤其是激光能量控制不当(比如能量过高),会在切割路径两侧留下深度 2-3μm 的热损伤层。 e.芯片粘贴(Die Bonding) 芯片粘贴是把芯片粘在引线框架或基板上,这个环节的应力来自 “导电胶 / 绝缘胶的固化收缩”。比如环氧导电胶,在 150℃固化时会有 2-3% 的体积收缩,这种收缩会对芯片产生 “拉扯应力”—— 如果胶层不均匀(比如局部胶厚差超过 10μm),应力会集中在胶层薄的区域,导致芯片边缘开裂。 更危险的是 “空心粘贴”,胶层里有气泡(直径>50μm),固化时气泡受热膨胀,冷却后收缩,会在气泡上方的芯片区域产生局部应力集中,形成 “隐形微裂纹”,这种裂纹在电测时完全看不出来,只有热循环时才会扩展。 f.引线键合(Wire Bonding) 引线键合(比如金丝键合)需要在芯片焊垫上施加压力(10-50gf)和超声波能量,同时加热(150-250℃)。这个过程中,三个因素会导致开裂。 (1)键合压力过大 比如把 25gf 的压力调成 40gf,超过了薄芯片(50μm)的承载极限,会在焊垫下方形成 “压痕裂纹”; (2)温度不均匀 键合台局部温度过高(比如温差超过 10℃),芯片上下表面形成热应力梯度,导致翘曲开裂; (3)焊垫边缘应力集中 如果键合点靠近芯片边缘(距离<50μm),压力会传递到芯片边缘,引发边缘裂纹。  2、材料与设计因素 芯片强度是研究芯片碎裂的最重要参数。芯片强度各不相同,只有强度最低的才最容易碎裂失效。强度分布范围很广,那些最"脆弱"的芯片碎裂时的强度只相当于芯片平均强度的几分之一。因此只需设法将最"脆弱"芯片的强度提高或者予以剔除,就能从根本上提高芯片整体强度。 材料缺陷也是导致芯片裂纹(Die Crack)的重要原因,包括: a.晶格缺陷 在晶体生长过程中产生的不完美结构; b.杂质污染 制造过程中引入的杂质原子; c.表面划痕 工艺处理过程中造成的机械损伤 设计方面的因素也不容忽视,如果半导体芯片的设计出现问题,比如结构过于复杂、焊点设计不合理等,都可能导致芯片更容易发生裂纹。 3、环境应力因素 外界环境因素会加剧芯片裂纹的产生和扩展: a.温度变化 剧烈的温度变化会导致材料热胀冷缩,产生热应力。 b.机械振动 运输或使用过程中的振动可能引发裂纹扩展。 c.湿度影响 封装树脂耐湿性差会导致产品吸湿,当封装体在环境温度剧变时,内部水分急剧汽化,当蒸汽压力大于封装树脂与芯片、载片以及框架表面之间的粘接力时,就会使它们的界面之间出现剥离现象,严重时还会导致封装树脂或芯片出现裂纹。  五、芯片裂纹(Die Crack)分析检测难点 在做芯片裂纹(Die Crack)失效分析时最让人头疼的就是芯片裂纹(Die Crack)在电性能测试(ICT、FT 测试)中根本查不出来 —— 只要微裂纹没延伸到焊垫或引线区域,不影响电流通路,电测就会判定为 “合格”。但这些 “看似合格” 的芯片,在客户端使用时,一旦经历温度变化,就会瞬间失效。 这背后的核心原因是热应力导致裂纹扩展。在高低温循环测试(比如 - 40℃~125℃,100 次循环)中,封装里的不同材料因 CTE 差异,会产生周期性的膨胀和收缩:塑封料膨胀时会挤压芯片,收缩时会拉扯芯片;引线框架的形变也会传递应力到芯片上。这些反复的热应力,会让原本的微裂纹以 “每天 1-2μm” 的速度扩展,直到裂纹贯穿芯片,切断电流通路,电性能才会失效。  六、解决芯片裂纹(Die Crack)不良的方法 通过上面第四大点分析出的芯片裂纹(Die Crack)的来源,我们可以有针对性地调整工艺,把芯片裂纹(Die Crack)率压到最低。结合之前在“安世半导体”做失效分析时的一些实践,分享几个经过验证的有效方案给大家参考: 1、晶圆减薄(Wafer Thinning) 把传统的 “纯机械研磨” 改成 “机械研磨 + 化学机械抛光(CMP)”:先用粗砂轮把晶圆减薄到目标厚度 + 20μm,再用 CMP(研磨液含二氧化硅颗粒和化学试剂)去除表面 20μm 的损伤层。这样处理后,硅片表面粗糙度能从机械研磨的 50nm 降到 1nm 以下,微裂纹密度直接从 100 个 /cm² 降到 0.1 个 /cm² 以下。某大厂的实践显示,改用 CMP 后,后续切割环节的开裂率从 8% 降到了 0.5%。 2、晶圆切割(Wafer Dicing) 对薄晶圆(<100μm),优先用 “激光半切 + 机械分离” 工艺:用 UV 激光在晶圆表面切出深度为晶圆厚度 1/2 的槽(比如 50μm 厚晶圆切 25μm 深),然后用机械推杆轻轻分离芯片。这种方式既没有机械刀片的挤压,也没有激光全切的热损伤,芯片边缘崩边率能控制在 0.1% 以内。如果必须用机械切割,要定期更换金刚石刀片(每切割 50 片晶圆换一次),并把切割压力控制在 30N 以下。 3、芯片粘贴(Die Bonding) 选择 “低模量环氧胶”(模量<5GPa,传统胶模量 10-15GPa),模量越低,固化收缩时产生的拉扯应力越小;同时,粘贴前对胶层进行真空脱泡(真空度 - 95kPa,保持 10 分钟),确保胶层气泡率<1%。某封装厂用这种方案后,粘贴环节的开裂率从 3% 降到了 0.2%。 4、引线键合(Wire Bonding) 键合前要校准键合压力(用压力传感器校准,误差<±1gf),并根据芯片厚度调整压力(50μm 厚芯片用 15-20gf,100μm 厚芯片用 25-30gf);同时,定期校准键合台温度(温差控制在 ±2℃),避免局部过热。另外,把键合点距离芯片边缘的距离控制在≥100μm,避开边缘应力集中区。  七、芯片裂纹(Die Crack)失效分析流程 因为芯片裂纹(Die Crack)不良问题是一个比较典型的失效模式,所以我们在分析过程中是需要系统而全面的,确保每一个细节都不被忽视,以下分析流程用一个实例给大家展示: 1、外观检查 利用高倍显微镜对样品的正反面进行了细致的外观检查,发现背面焊点存在异常,而其他表面未见异常。这一发现就会给出一个提示信号,问题可能出在焊接过程中或材料本身的缺陷。  2、X-Ray分析 刚开始先做一些无损分析,初步确认问题点。通过X-ray检查,可以发现样品顶部金线有异常凹陷,这是导致焊点异常的直接原因。X-Ray分析能够穿透材料表面,揭示内部结构的异常,这对于确定失效模式至关重要。  3、电性能测试 不良样品的电性能测试结果显示Pin8与Pin9之间存在短路,通过这一步就可证实在第一步做”外观检查“时的初步判断:短路可能是由于焊接不良或材料缺陷导致的电连接异常。  4、开封检查 从这一步开始,就是做的有损分析了。不良样品开封后,进一步发现芯片本身存在开裂现象,这是导致测试异常的根本原因。开封检查是失效分析中的关键步骤,它允许我们直接观察到芯片内部的物理损伤。  5、微观分析 利用扫描电子显微镜(SEM)对开裂区域进行了微观分析,观察到裂纹的形态和分布,以及可能的裂纹起源点。SEM分析能够提供高分辨率的图像,帮助我们理解裂纹的形成机制。 6、材料分析 对芯片材料进行了化学成分分析,以确定是否存在材料不纯或成分不均匀的问题。这些因素都可能导致材料的脆性增加,从而引发开裂。 7、热力学分析 通过热力学分析,我们评估了芯片在不同温度下的膨胀和收缩行为,以及这些热力学特性如何影响芯片的机械稳定性。 8、力学性能测试 对芯片进行了力学性能测试,包括拉伸、压缩和弯曲测试,以评估其抗裂性能。这些测试有助于我们了解芯片在实际使用条件下的力学响应。 9、环境应力筛选(ESS) 通过环境应力筛选,我们模拟了芯片在实际使用中可能遇到的各种环境条件,以评估其在极端条件下的可靠性。 通过这一单芯片裂纹(Die Crack)失效分析,可总结出:芯片开裂是导致测试异常的根本原因。这一发现不仅为客户解决了眼前的问题,也为其后续的产品改进提供了方向。  八、芯片裂纹(Die Crack)失效的建议 为了有效的避免此类失效会流入市场,导致在客户端发生客诉问题,我们应该从以下四个方面着手进行干预,以避免或是减少芯片裂纹(Die Crack)失效的不良案例,从而提升产品品质: 1、加强原材料质量控制 从源头上确保芯片材料的均匀性和可靠性,减少因材料缺陷导致的芯片裂纹(Die Crack)风险。 2、优化封装工艺 调整封装过程中的温度、压力等参数,减少热应力和机械应力对芯片的影响。 3、增强设计强度 在芯片设计阶段考虑更多的应力因素,增强芯片结构的抗裂性能。 4、定期进行可靠性测试 通过定期的可靠性测试,及时发现潜在的失效风险,减少产品在市场中的失效率。  九、写在最后面的话 因为“芯片裂纹(Die Crack)”失效模式它是与单晶硅的脆性本质直接相关,其失效可能隐匿于晶圆减薄、切割、贴装及键合等应力工艺环节。由于裂纹初期可能不显著影响电学性能,需通过高低温热循环实验加速裂纹扩展——不同材料热膨胀系数差异产生的热应力,会促使微裂纹扩展至可见程度,最终影响器件可靠性。当前行业正探索激光切割、化学机械抛光(CMP)等低应力工艺,以及通过离子注入增强硅片机械强度的新技术,以减少工艺损伤。 所以,半导体封装中芯片裂纹(Die Crack)的不良是一个复杂的多物理场耦合问题,根源在于机械应力和热应力。解决这一问题需要一个系统性的工程方法,贯穿于产品设计、材料选型、工艺制程和可靠性验证的全过程。通过综合运用先进的分析工具(如SAM)和科学的实验设计,可以有效地定位根本原因并实施改进,最终提升产品的良率和长期可靠性。 |